Flip-Flop

Dalam elektronik ,

sebuah flip-flop atau latch adalah sirkuit yang

memiliki dua pernyataan yang stabil dan dapat digunakan untuk menyimpan

informasi pernyataan. Sirkuit dapat dibuat untuk mengubah keadaan

dengan sinyal diterapkan ke satu atau lebih input kontrol dan akan memiliki

satu atau dua output. Ini adalah elemen penyimpanan dasar dalam logika sekuensial . Flip-flops

dan latches sebuah blok bangunan fundamental dari elektronika digital sistem

yang digunakan dalam komputer, komunikasi, dan jenis lain dari sistem.

Flip-flops dan latches yang digunakan sebagai

elemen penyimpanan data. Seperti penyimpanan data dapat digunakan

untuk penyimpanan pernyataan , dan

seperti sirkuit digambarkan sebagai logika sekuensial . Ketika digunakan dalam sebuah mesin finite-state ,

output dan pernyataan selanjutnya tergantung tidak hanya pada masukan saat ini,

tetapi juga pada kondisi saat ini (dan karenanya, input sebelumnya). Hal

ini juga dapat digunakan untuk menghitung pulsa, dan untuk sinkronisasi

bervariasi tepat waktu sinyal input ke beberapa sinyal referensi waktu.

Flip-flops dapat berupa sederhana (transparan

atau buram) atau clocked (sinkron atau tepi-dipicu); yang sederhana

biasa disebut latches. Kata latch ini terutama digunakan untuk elemen

penyimpanan, sedangkan perangkat clocked yang digambarkan sebagai flip-flops.

Sejarah

Flip-flop

skema dari Eccles dan Yordania paten yang diajukan tahun 1918, yang ditarik

sebagai kaskade amplifier dengan jalur umpan balik positif, dan yang lain

sebagai pasangan lintas digabungkan simetris

Elektronik flip-flop pertama diciptakan pada 1918 oleh William Eccles dan FW Jordan . Ini adalah awalnya disebut sirkuit memicu Eccles-Yordan dan terdiri dari dua elemen aktif ( tabung vakum ). sirkuit tersebut dan versi mereka Transistorized yang umum di komputer bahkan setelah pengenalan sirkuit terpadu , meskipun flip-flops yang terbuat dari gerbang logika juga umum sekarang.

Awal flip-flops dikenal beragam

sebagai sirkuit memicu atau multivibrators . Multivibrator

adalah sebuah sirkuit dua-pernyataan, mereka datang dalam beberapa varietas,

berdasarkan apakah masing-masing pernyataan stabil atau tidak: sebuah multivibrator

astabil tidak stabil dalam keadaan baik, sehingga ia bertindak sebagai

osilator relaksasi, sebuah monostable multivibratormembuat pulsa

sementara dalam keadaan tidak stabil, kemudian kembali ke keadaan stabil, dan

dikenal sebagai satu-menembak , sebuah multivibrator

bistable memiliki dua pernyataan yang stabil, dan ini yang biasanya

dikenal sebagai flip-flop.Namun, istilah ini telah agak variabel,

historis. Sebagai contoh:

§ 1942

- Multivibrator astabil menyiratkan: "Rangkaian Multivibrator (Gambar 7-6)

agak mirip dengan rangkaian flip-flop, tapi kopling dari anoda satu katup ke

jaringan yang lain adalah dengan sebuah kondensor saja, sehingga kopling tidak

dipertahankan dalam kondisi mapan ".

§ 1942

- Multivibrator sebagai rangkaian flip-flop khusus: ". Sirkuit seperti itu

dikenal sebagai 'pemicu' atau sirkuit 'flip-flop' dan penting yang sangat besar

paling awal dan paling terkenal sirkuit ini adalah multivibrator

tersebut."

§ 1943

- flip-flop sebagai satu-shot generator pulsa: "Perlu dicatat bahwa

perbedaan esensial antara dua flip-flop-katup dan Multivibrator adalah bahwa

flip-flop memiliki salah satu katup bias untuk cutoff."

§ 1949

- monostable sebagai flip-flop: ". Multivibrators monostabil juga telah

disebut 'flip-flops'"

§ 1949

- monostable sebagai flip-flop: "... flip-flop adalah multivibrator

monostable multivibrator dan biasa adalah multivibrator astabil."

Menurut PL Lindley, seorang JPL insinyur,

flip-flop jenis dibahas di bawah (RS, D, T, JK) pertama kali dibahas dalam

1954 UCLAkursus

desain komputer oleh Montgomery Phister, dan kemudian muncul dalam

bukunya Logical Desain Digital Komputer. Lindley pada waktu

itu bekerja di Hughes Aircraft bawah Dr Eldred Nelson, yang telah menciptakan

istilah untuk JK flip-flop yang mengubah pernyataan ketika kedua input berada

di. Nama-nama lainnya yang diciptakan oleh Phister. Mereka sedikit

berbeda dari beberapa definisi yang diberikan di bawah ini. Lindley

menjelaskan bahwa ia mendengar cerita dari flip-flop JK dari Dr Eldred Nelson,

yang bertanggung jawab untuk coining istilah saat bekerja di Hughes

Aircraft . Flip-flops digunakan di Hughes pada saat

itu semua jenis yang kemudian dikenal sebagai JK. Dalam merancang suatu

sistem logis, Dr Nelson ditetapkan huruf untuk flip-flop input sebagai berikut:

# 1: A & B, # 2: C & D, # 3: E & F, # 4: G & H, # 5: J & K.

Nelson menggunakan notasi " j -masukan

"dan" k -masukan "dalam permohonan paten

diajukan pada tahun 1953.

Implementasi

Flip-flops dapat berupa sederhana (transparan

atau asinkron) atau clocked (sinkron);. Transparan yang biasanya disebut latches Kata latch ini terutama digunakan untuk elemen

penyimpanan, sedangkan perangkat clocked digambarkan sebagai flip-flops .

Sederhana flip-flops dapat dibangun sekitar

sepasang lintas digabungkan unsur pembalik: tabung vakum , transistor bipolar ,transistor efek medan , inverter , dan

pembalik

gerbang logika semuanya telah digunakan dalam rangkaian

praktis. Perangkat clocked secara khusus dirancang untuk sistem

sinkron; perangkat seperti mengabaikan input mereka kecuali pada transisi dari

sinyal clocked khusus (dikenal sebagai clockeding, berdenyut, atau nyala). Clockeding menyebabkan flip-flop untuk perubahan baik atau

mempertahankan sinyal output didasarkan pada nilai-nilai sinyal masukan pada

transisi. Beberapa flip-flops

keluaran perubahan pada meningkatnya tepi dari jam, yang lain di tepi jatuh.

Sejak tahap penguatan dasar adalah pembalik,

dua tahap dapat dihubungkan dalam suksesi (sebagai kaskade) untuk membentuk

penguat non-pembalik dibutuhkan. Dalam konfigurasi ini, masing-masing penguat

dapat dianggap sebagai suatu jaringan umpan balik yang aktif pembalik untuk

penguat pembalik lainnya. Jadi dua tahap yang terhubung dalam loop

non-pembalik meskipun diagram rangkaian biasanya digambar sebagai sepasang

lintas digabungkan simetris (kedua gambar pada awalnya diperkenalkan dalam paten Eccles-Yordania).

Flip-flop jenis

Flip-flops dapat dibagi menjadi jenis umum: SR ("set-ulang"), D ("Data" atau "penundaan" ), T ("beralih"),

dan JK tipe yang umum. Perilaku

jenis tertentu dapat digambarkan oleh apa yang disebut persamaan karakteristik,

yang berasal dari "berikutnya" (yaitu, setelah pulsa clocked

berikutnya) output, Q n e x t ,

dalam hal sinyal input (s) dan / atau arus keluaran, Q .

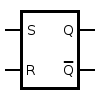

mengatur ulang-Sederhana

latches

SR latch NOR

SR latch, dibangun dari sepasang cross-digabungkan NOR gerbang (gambar animasi). Merah dan hitam berarti logis '1 'dan

'0', masing-masing.

Bila menggunakan gerbang statis sebagai blok

bangunan, latches paling mendasar adalah sederhana SR latch , dimana S dan R berdiri untukmengatur dan me-reset . Hal ini dapat dibangun dari sepasang

cross-digabungkan NOR gerbang logika . Bit disimpan hadir pada output ditandai Q.

Sementara input S dan R keduanya rendah, umpan balik mempertahankan

Q dan Q output dalam keadaan konstan, dengan Q komplemen

dari Q. Jika S ( Set )

adalah berdenyut tinggi sementara R ( Ganti ) diadakan

rendah, maka output Q dipaksa tinggi, dan tetap tinggi ketika S kembali ke

rendah, sama, jika R adalah berdenyut tinggi sementara S adalah diadakan

rendah, maka output Q dipaksa rendah, dan tetap rendah ketika R kembali ke

rendah.

|

Simbol untuk NOR

latch SR

|

||||||||||||||||||||||||||||||

R = S = 1 kombinasi disebut kombinasi dibatasi atau dilarang pernyataan karena,

baik sebagai gerbang NOR kemudian nol output, rusak persamaan logis Q = tidak Q . Kombinasi ini juga tidak tepat dalam

rangkaian di mana kedua input

bisa pergi rendah secara bersamaan (yaitu

transisi dari dibatasi untuk tetap ). Output akan mengunci pada 1 atau 0 tergantung

pada hubungan propagasi waktu antara gerbang (a kondisi lomba ). Pada

implementasi tertentu, itu juga bisa menyebabkan lagi ringings (teredam osilasi )

sebelum output mengendap, dan dengan demikian menghasilkan nilai ditentukan

(kesalahan) di frekuensi tinggi sirkuit digital. Meskipun

kondisi ini biasanya dihindari, dapat berguna dalam beberapa aplikasi.

Untuk mengatasi kombinasi terbatas, seseorang

dapat menambahkan gerbang ke input yang akan dikonversi (S, R) = (1,1) ke

salah satu non-dibatasi kombinasi. Itu bisa:

§ Q = 1 (1,0) - disebut sebagai latch S-

§ Q = 0 (0,1) - disebut sebagai latch R-

§ Menjaga pernyataan (0,0) - disebut sebagai latch E-

Karakteristik: Q + = R'Q + R atau Q + S = R'Q

+ S.

SR latch NAND

Sebuah SR latch

Ini adalah model alternatif dari SR latch

sederhana yang dibangun dengan NAND (tidak DAN ) gerbang logika . Mengatur dan me-resetsekarang

menjadi sinyal aktif rendah, dinotasikan S dan R masing-masing. Jika

tidak, operasi identik dengan SR latch. Secara

historis, SR -latches telah dominan meskipun

ketidaknyamanan notasi dari aktif-rendah input.

|

Simbol untuk SRlatch NAND

|

||||||||||||||||||||||||||||||||||||||||||

JK latches

Latches JK jauh lebih sedikit digunakan

dibandingkan dengan JK flip-flop . Latches

JK mengikuti state table berikut:

JK latches tabel kebenaran

|

||||

J

|

K

|

T berikutnya

|

Komentar

|

|

0

|

0

|

T

|

Tidak ada perubahan

|

|

0

|

1

|

0

|

Ulang

|

|

1

|

0

|

1

|

Set

|

|

1

|

1

|

T

|

Beralih

|

|

Oleh karena itu, latches JK adalah SR latch

yang dibuat untuk beralih output

ketika melewati kombinasi terbatas 11. Berbeda dengan flip-flop

JK, 11 masukan kombinasi untuk latch JK tidak berguna karena tidak ada jam yang

mengarahkan Toggling.

transparansi

gated latches dan bersyarat

Latches yang dirancang untuk menjadi transparan. Artinya, perubahan sinyal masukan langsung

menyebabkan perubahan dalam output; ketika beberapa transparan latches mengikuti satu sama lain, dengan

menggunakan sinyal clocked yang sama, sinyal dapat merambat melalui semua itu

sekaligus. Atau, logika tambahan dapat ditambahkan ke latch

transparan sederhana untuk membuat non-transparan atau buram ketika input lain (sebuah

"mengaktifkan" masukan) tidak menegaskan. Dengan

mengikuti transparan-tinggi latches

dengan transparan-rendah(atau buram-tinggi latch), master-slave flip-flop

diimplementasikan.

SR latch

gated

Sebuah SR latch diagram sirkuit dibangun dari NOR gated gerbang.

Sebuah SR latch sinkron (kadang-kadang clocked SR flip-flop )

dapat dibuat dengan menambahkan tingkat kedua dari gerbang NAND ke SR latch

terbalik (atau tingkat kedua dari DAN gerbang ke SR latch langsung). Gerbang

ekstra lanjut membalikkan input sehingga yang sederhana SR latch

menjadi SR latch gated (dan SR latch sederhana akan berubah menjadi gated SR latch

dengan mengaktifkan terbalik).

Dengan E tinggi ( mengaktifkan benar), sinyal dapat melewati gerbang input

ke latches dienkapsulasi; kombinasi semua sinyal kecuali untuk (0,0) = tahan kemudian segera mereproduksi pada (Q, Q output),

yaitu latch transparan .

Dengan E rendah ( mengaktifkan palsu) latch tertutup (buram) dan

tetap di pernyataan itu ditinggalkan E terakhir kali tinggi.

Yang memungkinkan input

kadang-kadang sinyal clocked , tetapi lebih sering membaca atau menulis

strobo.

|

Simbol untuk SR

latch gated

|

||||||||

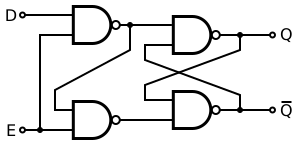

latches

gated D

Sebuah latch D-tipe transparan berdasarkan SR latch

NAND

Sebuah latches D gated didasarkan pada NOR latch SR

Latches ini memanfaatkan fakta bahwa dalam

dua kombinasi input aktif (01 dan 10) dari SR latch gated R adalah komplemen

dari S. Tahap masukan mengkonversi NAND dua masukan pernyataan D (0 dan 1)

untuk kedua kombinasi input untuk berikutnya SR latch

dengan membalik sinyal input data. Keadaan rendah dari mengaktifkan sinyal menghasilkan tidak aktif

"11" kombinasi. Jadi D latch-gated dapat dianggap sebagai satu-masukan latch SR sinkron . Konfigurasi

ini mencegah dari penerapan kombinasi terbatas pada input. Hal

ini juga dikenal sebagai gerendel transparan , data yang latches ,

atau hanya gated latch . Ia memiliki data yang input dan mengaktifkan sinyal (kadang-kadang disebut jam , atau kontrol ). Kata transparan berasal

dari fakta bahwa, ketika input mengaktifkan aktif, sinyal merambat langsung

melalui sirkuit, dari D input ke output Q.

Transparan latches biasanya digunakan sebagai

port I / O atau dalam sistem asinkron, atau di sinkron dua-fase sistem ( sistem sinkron yang

menggunakan fase dua jam ), di mana dua latches operasi pada jam

berbeda fase mencegah transparansi data seperti pada master- budak flip-flop.

Latches tersedia sebagai sirkuit terpadu ,

biasanya dengan beberapa latches per keping. Sebagai

contoh, 74HC75 adalah gerendel transparan empat kali lipat dalam seri 7400 .

|

Simbol untuk latch D

gated

|

|||||||||||||||||||||||||||

Tabel kebenaran menunjukkan bahwa ketika e nable / c masukan kunci adalah 0, input D tidak

memiliki efek pada output. Ketika E / C yang tinggi, output sama dengan

D.

Earle

latches

Earle menggunakan input latch Aktifkan pelengkap: Aktifkan Rendah aktif

(E_L) dan Aktifkan aktif Tinggi (E_H)

Desain klasik gated latch memiliki beberapa

karakteristik yang tidak diinginkan. Mereka membutuhkan rel ganda logika atau

inverter. Propagasi input-ke-output dapat memakan waktu hingga tiga

keterlambatan gerbang. Propagasi input-ke-keluaran tidak konstan -

beberapa output mengambil dua penundaan gerbang sementara yang lain mengambil

tiga.

Desainer mencari alternatif. Sebuah

alternatif yang sukses adalah gerendel Earle Ini hanya membutuhkan masukan data tunggal,

dan output yang mengambil dua penundaan konstan gerbang. Selain

itu, tingkat gerbang dua latches Earle dapat digabungkan dengan dua tingkat

terakhir gerbang sirkuit mengemudi gerendel. Penggabungan

fungsi latches dapat menerapkan latch tanpa penundaan gerbang tambahan.

Latches Earle adalah bahaya gratis. Jika

tengah gerbang NAND dihilangkan, maka salah satu mendapat polaritas latches terus ,

yang umum digunakan karena tuntutan logika kurang. Sengaja skewing sinyal clocked dapat menghindari bahaya.

flip-flop D

D flip-flop simbol

D flip-flop digunakan secara luas. Hal

ini juga dikenal sebagai Data atau keterlambatan flip-flop.

Flip-flop D menangkap nilai dari input D-di

sebagian tertentu dari siklus clocked (seperti meningkatnya tepi jam). Bahwa

nilai ditangkap menjadi output Q. Di lain waktu, output Q tidak berubah.. D flip-flop dapat dilihat sebagai sel memori, tahan orde nol ,

atau delay line .

Tabel kebenaran:

Jam

|

D

|

T berikutnya

|

Meningkatnya

tepi

|

0

|

0

|

Meningkatnya

tepi

|

1

|

1

|

Meningkatnya

Non-

|

X

|

T

|

Kebanyakan tipe-D flip-flops di IC memiliki

kemampuan untuk dipaksa untuk mengatur atau mengatur ulang pernyataan (yang

mengabaikan D dan masukan jam), banyak seperti flip-flop SR. Biasanya,

S ilegal = R = 1 kondisi diselesaikan dalam D-flip-flop. Dengan

menetapkan S = R = 0, flip-flop dapat digunakan sebagai dijelaskan di atas.

Masukan

|

Output

|

||||

S

|

R

|

D

|

>

|

T

|

Q

'

|

0

|

1

|

X

|

X

|

0

|

1

|

1

|

0

|

X

|

X

|

1

|

0

|

1

|

1

|

X

|

X

|

1

|

1

|

Ini flip-flops sangat berguna, karena mereka

membentuk dasar untuk register geser , yang merupakan bagian penting dari perangkat

elektronik banyak. Keuntungan dari D flip-flop atas

"latches transparan" tipe-D adalah bahwa sinyal pada pin input D

ditangkap saat flip-flop adalah clockeded, dan perubahan berikutnya pada input

D akan diabaikan sampai berikutnya jam acara. Pengecualian

adalah bahwa beberapa flip-flops memiliki "reset" input sinyal, yang

akan mengatur ulang Q (nol), dan mungkin baik asinkron atau sinkron dengan jam.

Rangkaian di atas menggeser isi register ke

kanan, satu bit pada setiap posisi transisi aktif jam. X

masukan digeser ke posisi bit paling kiri.

Klasik

positif-tepi-dipicu D flip-flop

Sebuah positif-tepi-dipicu D flip-flop

Sirkuit ini cerdas terdiri dari dua tahap dilaksanakan oleh SR NAND latches . Tahap input (dua latches di sebelah kiri)

memproses sinyal clocked dan data untuk memastikan sinyal input yang benar

untuk tingkat keluaran (latches tunggal di sebelah kanan). Jika

jam rendah, kedua sinyal output dari tahap input tinggi tanpa input data,

output latch terpengaruh dan menyimpan keadaan sebelumnya. Ketika

perubahan sinyal clocked dari rendah ke tinggi, hanya satu dari tegangan output

(tergantung pada sinyal data) pergi rendah dan set / reset latch output: jika D

= 0, output yang lebih rendah menjadi rendah, jika D = 1, Output atas menjadi

rendah. Jika sinyal clocked terus tinggal tinggi, output tetap

menyatakan mereka terlepas dari masukan data dan keluaran latch memaksa untuk

tinggal di pernyataan yang sesuai sebagai masukan nol logis tetap aktif

sementara jam sudah tinggi. Oleh karena itu peran latch output untuk

menyimpan data hanya saat jam rendah.

Rangkaian ini erat terlatches dengan latches D gated baik sebagai sirkuit mengkonversi dua

pernyataan D masukan (0 dan 1) untuk dua kombinasi masukan (01 dan 10) untuk

output SR latch dengan membalik sinyal masukan data

(baik sirkuit perpecahan D sinyal tunggal dalam dua komplementer S dan R sinyal). Perbedaannya

adalah bahwa dalam latches D gated sederhana gerbang NAND logis yang digunakan

sementara di tepi-positif dipicu D flip-flop SR NAND

latches yang digunakan untuk tujuan ini. Peran

ini latches adalah untuk "mengunci" aktif memproduksi output tegangan

rendah (nol logis); sehingga positif-tepi-dipicu D flip-flop dapat dianggap

sebagai latch D gated dengan gerbang masukan terkunci.

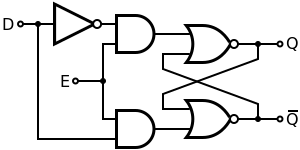

Guru-budak

pulsa-dipicu D flip-flop

Sebuah master-slave flip-flop D dibuat dengan

menghubungkan dua gated D latches dalam seri, dan membalik memungkinkan masukan untuk salah satu dari mereka. Hal

ini disebut master-budak karena latches kedua dalam seri hanya perubahan dalam

menanggapi perubahan di latch (master) pertama.

Istilah pulsa-dipicu berarti bahwa data yang dimasukkan pada tepi

naik dari pulsa clocked, tetapi output tidak mencerminkan perubahan sampai tepi

jatuh dari pulsa clocked.[ meragukan mendiskusikan ]

Sebuah master-budak D flip-flop.Menanggapi di tepi negatif dari mengaktifkanmasukan (biasanya jam)

Sebuah pelaksanaan master-budak D flip-flop yang dipicu di tepi positif

dari jam

Untuk seorang budak master-positif-tepi

dipicu D flip-flop, ketika sinyal clocked rendah (0 logis) yang

"memungkinkan" dilihat oleh latches pertama atau "master" D

(sinyal clocked terbalik) tinggi (1 logis) . Hal

ini memungkinkan master "" latches untuk menyimpan nilai masukan

ketika sinyal clocked transisi dari rendah ke tinggi. Sebagai

sinyal clocked berjalan tinggi (0 ke 1) yang terbalik "mengaktifkan"

dari latch pertama pergi rendah (1 sampai 0) dan nilai terlihat di input ke

latches master "terkunci". Hampir bersamaan, dua kali terbalik

"mengaktifkan" dari kedua atau "budak" D latch transisi

dari rendah ke tinggi (0 ke 1) dengan sinyal clocked. Hal

ini memungkinkan sinyal yang ditangkap di tepi terbit jam oleh sekarang latches

"dikunci" master untuk melewati latches "budak". Ketika

kembali ke sinyal clocked rendah (1 sampai 0), output dari latches

"budak" adalah "terkunci", dan nilai yang terlihat di tepi

terbit jam terakhir diadakan sedangkan "master" latches mulai

menerima baru nilai dalam persiapan untuk tepi jam berikutnya naik.

Dengan menghapus inverter paling kiri dalam

rangkaian di samping, flop D-flip yang lampunya di tepi jatuh dari sebuah sinyal clocked dapat diperoleh. Ini

memiliki tabel kebenaran seperti ini:

D

|

T

|

>

|

T berikutnya

|

0

|

X

|

Jatuh

|

0

|

1

|

X

|

Jatuh

|

1

|

Ujung-dipicu

elemen penyimpanan dinamis D

Sebuah alternatif fungsional efisien untuk

flip-flop D dapat dibuat dengan sirkuit yang dinamis selama itu adalah clockeded

cukup sering, sedangkan tidak benar flip-flop, masih disebut sebuah flip-flop

untuk peran fungsional. Sementara master-budak D elemen dipicu di

tepi sebuah jam, masing-masing komponennya dipicu oleh tingkat jam. "Ujung-dipicu

D flip-flop", seperti yang disebut meskipun tidak benar flip-flop, tidak

memiliki master-budak properti.

Edge-triggered D flip-flop sering

diimplementasikan dalam berkecepatan tinggi yang terintegrasi operasi

menggunakan logika dinamis. Ini berarti bahwa output digital yang

disimpan pada perangkat kapasitansi parasit saat perangkat tidak transisi. Ini

desain flip yang dinamis jepit juga memungkinkan sederhana ulang sejak operasi

ulang dapat dilakukan dengan hanya pemakaian satu atau lebih node internal. Sebuah

dinamis umum flip-flop variasi merupakan fase tunggal yang sejati jam (TSPC)

jenis yang melakukan operasi flip-flop dengan daya kecil dan pada kecepatan

tinggi. Namun, dinamis flip-flops biasanya tidak akan bekerja

pada kecepatan clocked statis atau rendah: dengan waktu yang cukup, jalur

kebocoran dapat debit kapasitansi

T flip-flop

Sebuah simbol sirkuit untuk T-jenis flip-flop

Jika input T adalah tinggi, T flip-flop

pernyataan perubahan ("matikan") setiap kali input clocked strobed. Jika

input T adalah rendah, flip-flop memegang nilai sebelumnya.Perilaku ini

dijelaskan oleh karakteristik persamaan :

T

|

T

|

T n e x t

|

Komentar

|

T

|

T n e x t

|

T

|

Komentar

|

|

0

|

0

|

0

|

tahan

pernyataan (tidak ada CLK)

|

0

|

0

|

0

|

Tidak

ada perubahan

|

|

0

|

1

|

1

|

tahan

pernyataan (tidak ada CLK)

|

1

|

1

|

0

|

Tidak

ada perubahan

|

|

1

|

0

|

1

|

beralih

|

0

|

1

|

1

|

Melengkapi

|

|

1

|

1

|

0

|

beralih

|

1

|

0

|

1

|

Melengkapi

|

|

Ketika T adalah terangkat tinggi, flip-flop

beralih membagi frekuensi clocked oleh dua, yaitu, jika frekuensi clocked 4

MHz, frekuensi output yang diperoleh dari flip-flop akan 2 MHz. Ini

"bagi dengan" fitur memiliki aplikasi dalam berbagai jenis digital counter . AT

flip-flop juga dapat dibangun menggunakan JK flip-flop (J & K pin yang

terhubung bersama-sama dan bertindak sebagai T) atau D flip-flop (T masukan dan

Q sebelumnya terhubung ke input D melalui gerbang XOR). AT

flip-flop juga dapat dibangun menggunakan ujung-dipicu D flip-flop dengan input

D yang makan dari output sendiri nya terbalik.

JK flip-flop

Sebuah simbol sirkuit untuk positif-tepi-dipicu JK flip-flop

JK flip-flop waktu diagram

JK flip-flop sirkuit diagram

JK flip-flop menambah perilaku dari SR

flip-flop (J = Set, K = Reset) dengan menafsirkan S = R = 1 kondisi sebagai

"flip" atau perintah beralih. Secara

khusus, kombinasi J = 1, K = 0 adalah perintah untuk mengatur flip-flop,

kombinasi J = 0, K = 1 adalah perintah untuk me-reset flip-flop, dan kombinasi

J = K = 1 adalah perintah untuk mengaktifkan flip-flop, yaitu mengubah output

untuk komplemen logis dari nilai saat ini. Mengatur

J = K = 0 TIDAK menghasilkan D flip-flop, melainkan, akan terus kondisi saat

ini. Untuk mensintesis D flip-flop, cukup menetapkan K sama

dengan komplemen dari J. Demikian pula, untuk mensintesis T flip-flop, mengatur

K sama dengan J. JK flip-flop karena flip-flop universal, karena dapat

dikonfigurasi untuk bekerja sebagai flip-flop SR, flip-flop D, atau T

flip-flop.

Persamaan karakteristik dari flip-flop JK

adalah:

dan tabel kebenaran yang sesuai adalah:

J

|

K

|

T berikutnya

|

Komentar

|

T

|

T berikutnya

|

J

|

K

|

Komentar

|

0

|

0

|

T

|

terus

pernyataan

|

0

|

0

|

0

|

X

|

Tidak

ada perubahan

|

0

|

1

|

0

|

ulang

|

0

|

1

|

1

|

X

|

Set

|

1

|

0

|

1

|

mengatur

|

1

|

0

|

X

|

1

|

Ulang

|

1

|

1

|

T

|

beralih

|

1

|

1

|

X

|

0

|

Tidak

ada perubahan

|

Metastabilitas

Flip-flops rentan terhadap masalah yang

disebut Metastabilitas ,

yang bisa terjadi ketika dua input, seperti data dan jam atau jam dan reset,

berubah pada waktu yang sama, seperti bahwa pernyataan yang dihasilkan akan

tergantung pada urutan peristiwa masukan . Ketika

order tidak jelas, dalam keterbatasan waktu yang tepat, hasilnya adalah bahwa

output mungkin berperilaku tak terduga, mengambil banyak kali lebih lama dari

biasanya untuk menetap pada satu pernyataan atau yang lain, atau bahkan

berosilasi beberapa kali sebelum menetap. Secara

teoritis, waktu untuk tenang tidak dibatasi. Dalam komputer sistem, Metastabilitas ini dapat menyebabkan

korupsi data atau crash program, jika pernyataan tidak stabil sebelum sirkuit

lain menggunakan nilainya; pada khususnya, jika dua jalur logis yang berbeda

menggunakan output dari flip-flop, satu jalan yang bisa menafsirkannya sebagai

0 dan yang lain sebagai 1 jika belum memutuskan untuk keadaan stabil,

menempatkan mesin menjadi pernyataan tidak konsisten.

pertimbangan Waktu

Setup dan

terus kali

Flip-flop setup, terus dan jam-untuk-output parameter waktu

Waktu setup adalah

jumlah waktu minimum sinyal data harus tetap stabil sebelum acara jam sehingga data yang andal sampel

oleh jam.Hal ini berlaku untuk sinkron sirkuit seperti

flip-flop.

Terus waktu adalah

jumlah waktu minimum sinyal data harus tetap stabil setelah acara jam sehingga data yang andal sampel. Hal

ini berlaku untuk sinkron sirkuit seperti

flip-flop.

Untuk meringkas: Waktu setup -> sayap Jam

-> Tahan waktu.

Para Metastabilitas di flip-flops dapat

dihindari dengan memastikan bahwa data dan input kontrol diadakan berlaku dan

konstan untuk periode tertentu sebelum dan sesudah pulsa clocked, yang disebut waktu setup (t su ) dan terus waktu (t h )

masing-masing. Saat-saat yang ditentukan dalam lembar data untuk

perangkat, dan biasanya antara beberapa nanodetik dan beberapa ratus

picoseconds untuk perangkat modern.

Sayangnya, tidak selalu mungkin untuk

memenuhi setup dan terus kriteria, karena flip-flop dapat dihubungkan ke sinyal

real-time yang bisa berubah setiap saat, di luar kendali desainer. Dalam

hal ini, yang terbaik perancang dapat lakukan adalah untuk mengurangi

kemungkinan kesalahan untuk tingkat tertentu, tergantung pada keandalan yang

diperlukan dari sirkuit. Salah satu teknik untuk menekan

Metastabilitas adalah untuk menghubungkan dua atau lebih flip-flops di rantai,

sehingga output dari masing-masing feed input data berikutnya, dan semua

perangkat berbagi jam umum. Dengan metode ini, probabilitas dari

peristiwa metastabil dapat dikurangi dengan nilai diabaikan, tetapi tidak

pernah sampai nol. Probabilitas Metastabilitas semakin dekat dan

lebih dekat ke nol sebagai jumlah flip-flop dihubungkan secara seri meningkat.

Jadi yang disebut metastabil-keras flip-flops

yang tersedia, yang bekerja dengan mengurangi setup dan terus kali sebanyak

mungkin, tapi bahkan ini tidak dapat menghilangkan masalah sama sekali. Hal

ini karena Metastabilitas lebih dari hanya masalah desain sirkuit. Ketika

transisi dalam jam dan data dalam waktu berdekatan, flip-flop dipaksa untuk

memutuskan mana terjadi peristiwa pertama. Namun

cepat kita membuat perangkat, selalu ada kemungkinan bahwa peristiwa input akan

begitu dekat bersama bahwa ia tidak dapat mendeteksi mana yang terjadi terlebih

dahulu. Oleh karena itu logis mustahil untuk

membangun sebuah sempurna metastabil-bukti flip-flop.

keterlambatan

Propagasi

Nilai lain waktu penting bagi sebuah

flip-flop (F / F) adalah delay jam-ke-keluaran (simbol umum dalam lembar data:

t CO ) atau delay propagasi (t P ), yang merupakan waktu flip-flop yang

diperlukan untuk mengubah output setelah clocked edge. Waktu

untuk transisi tinggi ke rendah (t PHL )

kadang-kadang berbeda dari waktu untuk transisi rendah ke tinggi (t PLH ).

Ketika Cascading F / Fs yang berbagi jam yang

sama (seperti dalam sebuah register geser ), penting untuk memastikan bahwa t CO dari sebelumnya F / F adalah lebih lama dari

waktu terus (t h ) dari flip-flop berikut, sehingga data hadir

pada masukan dari berhasil F / F adalah benar "bergeser" setelah tepi

aktif jam. Hubungan antara t CO dan t h biasanya dijamin jika F / Fs secara fisik

identik. Selanjutnya, untuk operasi yang benar, mudah untuk

memverifikasi bahwa periode jam harus lebih besar daripada jumlah t su + t h .

Generalisasi

Flip-flops dapat digeneralisasi dalam

setidaknya dua cara: dengan membuat mereka 1-dari-N bukan 1-dari-2, dan dengan

mengadaptasi mereka untuk logika dengan lebih dari dua pernyataan. Dalam

kasus-kasus khusus 1-of-3 encoding, atau multi-nilai logika terner ,

elemen-elemen ini dapat disebut sebagai flip-flap-jepit .

Dalam konvensional flip-flop, tepat satu dari

dua output komplementer adalah tinggi. Hal ini dapat digeneralisasi untuk elemen

memori dengan output N, tepat satu dari yang tinggi (alternatif, di mana

tepatnya salah satu dari N rendah). Oleh karena itu output selalu merupakan satu-panas (masing-masing satu-dingin ) representasi. Konstruksi

mirip dengan lintas digabungkan konvensional flip-flop, setiap output, ketika

tinggi, menghambat semua output lain. Atau, lebih atau kurang

konvensional flip-flop dapat digunakan, satu per output, dengan sirkuit

tambahan untuk pastikan hanya satu pada suatu waktu dapat menjadi kenyataan.

Lain generalisasi dari flip-flop konvensional

adalah elemen memori untuk multi-nilai logika . Dalam

hal ini elemen memori mempertahankan persis salah satu pernyataan logika sampai

control input menginduksi perubahan. Selain itu, beberapa jam

bernilai juga dapat digunakan, yang mengarah ke transisi baru jam mungkin.